Document Number: AN12288

Rev. 0, 11/2018

# How to Migrate from QN902x/D to QN902x/E

Migration Instructions Based on SDK1.4.0

## 1. Introduction

There are two hardware versions available on NXP website for QN902x, which are QN902x/DY and QN902x/EY. QN902x/DY is with die version B2, while QN902x/EY is with die version B4.

Compared with QN902x/DY, the improvement for QN902x/EY is as following:

- Bootloader supports fast boot function

- Put stack patch into ROM to save 6k+ codes space

The E version is supported from SDK1.3.8. The SDK1.4.0 is the latest SDK package that is with bug fix from SDK1.3.9 and previous version and supports Bluetooth LE 4.0 and 4.2.

The advantage of SDK1.4.0 is as the following:

- Support Bluetooth LE 4.0 and 4.2

- Support both QN902x D version and E version

- Fixed the bugs found in SDK1.3.9

Based on the SDK1.4.0, the migration from QN902x/DY to QN902x/EY is elaborated here.

#### **Contents**

| 1. | Introduction                             | 1 |  |

|----|------------------------------------------|---|--|

|    | Software configuration                   |   |  |

|    | 2.1. Enable macro for B4 in usr_config.h |   |  |

|    | 2.2. Enable the library for B4           |   |  |

|    | Code size                                |   |  |

| 4. | Fast boot                                |   |  |

|    | 4.1. Enable fast boot                    | 5 |  |

| 5. | Hardware design                          |   |  |

| 6. | Software tool                            |   |  |

| 7. | Revision history                         | 7 |  |

## 2. Software configuration

The project 'prj\_qpps' is taken as an example to illustrate the details to support QN902x/EY, which resides in the SDK installation folder.

### 2.1. Enable macro for B4 in usr\_config.h

The following macro definition in usr\_config.h is used to enable the support of corresponding chip. CFG\_QN9020\_B4 is for the E version, CFG\_QN9020\_B2 is for the D version. Define CFG\_QN9020\_B4 to support E version.

```

// Select corresponding library file according to the chip version.

// The last marking letter of chip is 'E' for QN902x B4 and 'D' for QN902x B2.

#define CFG_9020_B4

```

Figure 1. Macro Definition

## 2.2. Enable the library for B4

In the Keil IDE project window, there are several libraries included in the lib folder. The lib with the letters B2 are for the D version chip, the letters B4 for the E version chip. The suffix 40 means the lib that supports Bluetooth LE 4.0, 42 means supporting 4.2. We need enable all the libraries that for b4, and disable b2 version libraries. This demo have 'qn\_ota\_b4.lib', 'Qn9020b4\_lib\_prepheral\_v42.lib' enabled.

#### **NOTE**

- $qn\_ota\_b4.lib$  is the lib for b4 version OTA feature, while  $qn\_ota\_b2.lib$  is the lib for b2 version.

- *Qn9020b4\_lib\_prepheral\_v42.lib* is the lib for b4 version BLE4.2 peripheral role.

The procedures is described below:

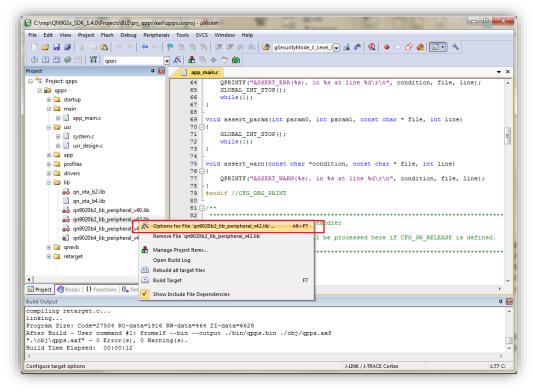

• Step1: Right click on the selected library file and, select the option item referring as in *Figure* 2.

Figure 2. Keil file Option

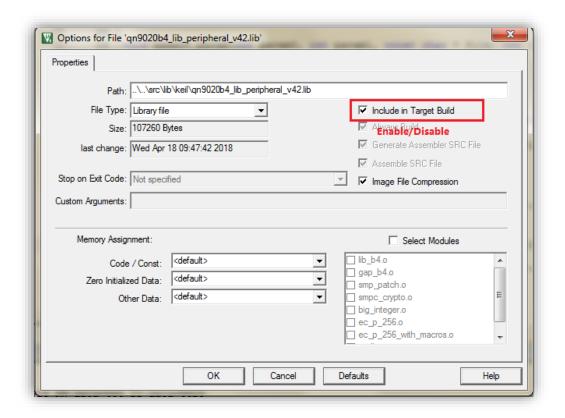

• Step2: Enable/Disable the library by clicking the check box referring as in *Figure* 3.

Figure 3. Enable/Disbale library

• Step3: Build the project and debug.

### 3. Code size

The patches for stack in SDK1.3.9 are put into the Rom of QN902x. The codes space is about 6 k bytes larger depending the combination between die version and Bluetooth LE version. The code size for each combination is illustrated in the table below:

Chip Bluetooth LE Demo project code size Library names version core version Code RO-data RW-data ZI-data gn9020b4 lib peripheral v42.lib **B4** Bluetooth LE 4.2 27504 1916 464 6628 gn9020b4 lib peripheral v40.lib Bluetooth LE 4.0 1644 412 5220 15676 qn9020b2\_lib\_peripheral\_v42.lib B2 Bluetooth LE 4.2 1932 492 33008 6768 gn9020b2\_lib\_peripheral\_v40.lib Bluetooth LE 4.0 21392 1664 452 5708

Table 1. Code size

#### **NOTE**

The keil compiler optimization level is level3(-O3).

The code size for B2 version is about 6 k bytes bigger than that with B4. For the application with several profiles enabled, the QN902x E version and the SDK with B4 lib enabled is recommended.

## 4. Fast boot

The QN902x E version supports the fast boot feature. The hardware pin (p2.6) is used to enable/disable the fast boot. When enabled by pulling the pin high, bootloader starts in the fast boot mode without the ISP waiting time(200 ms for 16 MHz crystal). Pull down the pin of P2.6 to perform the ISP operation.

#### 4.1. Enable fast boot

Following two steps are required to enable fast boot:

Step 1: Enable fast boot feature in Bootloader

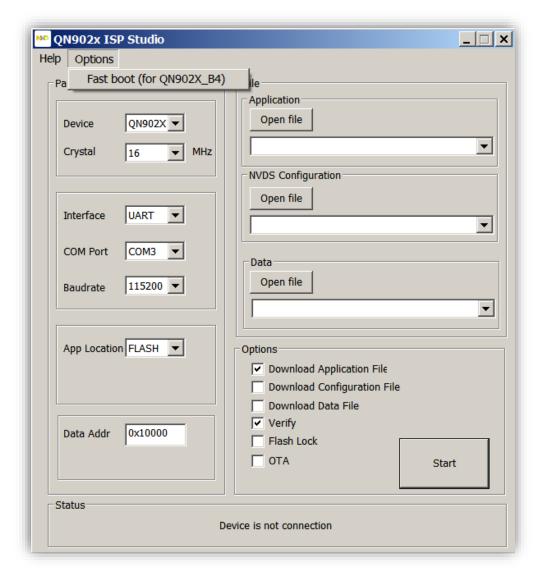

QN902x ISP Studio is a tool which can download application file, data file or configuration file into target chip. To enable the fast boot feature on E version, the fast boot command must be executed.

This command is hidden in Options menu on the top of ISP Studio window, which is illustrated in Figure 4. Click the command to enable the option, and download firmware by the tool, the fast boot feature is enabled in bootloader. Click the Options menu again to disable the fast boot, and performed the ISP firmware updating again, the fast boot feature is disabled in Bootloader.

NXP Semiconductors 5

Figure 4. ISP studio fast boot option

#### Step 2: Enable fast boot function

Pull the pin P2.6 to high, the fast boot function is enabled. Bootloader will bypass ISP function and boot from RAM after loading codes from flash.

## 5. Hardware design

There is no change on the functions of GPIO pins excet P2.6. To support fast boot, the pin should be pulled up to high and enable fast boot function in bootloader by ISP tool as described in Section 4.

## 6. Software tool

Two software tools, QBlue ISP Studio and QN902x production tool, are impacted when switching from D version to E version. The change is as following:

- a) There is more code space in the E version chip, the tool is revised to fit bigger image size.

- b) The option "Fast boot(for QN9020B4)" is added to support fast boot feature.

## 7. Revision history

Table 2. Revision history

| Revision number | Date    | Substantive changes |

|-----------------|---------|---------------------|

| 0               | 11/2018 | Initial release.    |

How to Reach Us:

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2018 NXP B.V.

Document Number: AN12288

Rev. 0 11/2018