# **AN13158**

# NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

Rev. 1.1 — 18 November 2022

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | NVT4557, NVT4558, NVT4858, Level Shifter, Level Translator, SD card, SIM card, Layout Guideline                                                                                                                                                                                                                     |

| Abstract    | The NVT4858 is an SD 3.0 compliant dual voltage level translator with auto-direction control. The NVT4557/4558 is a SIM SIO-7816 Smart Card compliant dual voltage level translator with auto-direction control. This application note details the layout guidelines to ensure the optimal operation of the device. |

# NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

#### **Revision history**

| Rev   | Date     | Description     |

|-------|----------|-----------------|

| v.1.1 | 20221118 | Added NVT4558   |

| v.1   | 20210701 | Initial version |

#### NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

#### 1 Introduction

High performance digital signals on modern microprocessors are designed using advanced CMOS process to take advantage of its low power consumption. However, CMOS logic has very fast edge rates in the range of 1 ns to 2 ns. PCB traces might exhibit ringing, signal degradation and reflection due to the effect of the signal's fast rise and fall time contributed by the PCB transmission characteristic.

This application note details the general PCB layout guidelines for High Speed Secure Digital (SD), and Smart Card (SIM) in NVT4858 and NVT4557/4558 voltage level shifter application to minimize signal integrity issues.

# 2 NVT4557/4558/4858 voltage-level translator layout guidelines

To ensure optimal performance and reliability of the device, the following PCB layout guidelines are recommended.

## 2.1 Power and ground

- · A minimum four-layer PCB stack-up is required.

- The level shifter and the card socket should be placed top of a solid, continuous ground plane.

- Preferably, the power for the level shifter should come directly from the power plane underneath it, but if the power trace must be used then the trace should be at least 20 mil wide.

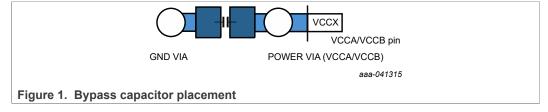

- Bypass capacitors of 0.1 μF should be placed as close as possible to VCCA and VCCB pins with a very short PCB trace.

#### 2.2 SD and SIM signals from host to level shifter

The SD interface high speed signals SD\_DAT[3:0], SD\_CDM and SD\_CLK are critical and require careful layout and consideration. These signals must be routed above a solid ground plane and should be routed with the following recommendations.

- Component Placement and Trace Impedance high frequency signals are sensitive to impedance changes and discontinuity introduced by vias. The level shifter and the card socket should be placed on the same layer as the Hot Controller. Placing these devices on the same layer helps to reduce the need to use vias with direct routing between these devices. The PCB traces should be routed with 50 Ω characteristic impedance or close to it to reduce transmission effect. The round-trip delay of the PCB traces should be less than the rise/fall times of the signal driver. If the PCB traces are longer than the rise/fall times, then series termination resistors can be used to minimize signal reflection.

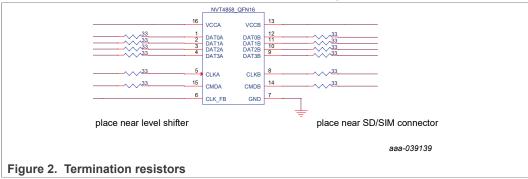

- Series Termination and Placement if series termination resistors are to be used, the suggested values are 22  $\Omega$  to 33  $\Omega$ . The termination resistors on the Host Controller

AN13158

#### NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

side of the level shifter should be placed close to the level shifter. The termination resistors on the card side of the level shifter should be placed close to the card socket.

- PCB trace separation SD clock and data signals carry high frequency fast rise and fall time signals. Any low capacitive impedance path existed between two traces creates a path for one signal to couple onto another signal next to it. For this reason, SD clock and data must be separate from one another with the following spacing constraint.

- SD\_CLK > 2 times the high of SD\_CLK to the ground plane underneath it. SD\_DATA[3:0] > 1.5 times the high of SD\_CLK to the ground plane underneath it. SD\_CMD > 1.5 times the high of SD\_CLK to the ground plane underneath it.

- Trace Routing when routing the PCB traces, it is critical to keep the trace width the same to keep the trace impedance constant from the driver to the receiver. Any trace width deviation creates impedance mismatch and creates signal reflection. Avoid using 90-degree angle and use a 45-degree bend when the trace must be routed perpendicularly.

- PCB Trace length matching to minimize the skew between traces, route them with the same length.

#### 2.3 SD and SIM signals from level shifter to card socket

The SD interface high speed signals SD\_DAT[3:0], SD\_CDM and SD\_CLK are critical and require careful layout and consideration. These signals must be routed above a solid ground plane and should be routed with the following recommendations.

- Component Placement and Trace Impedance component placement and trace impedance should follow the guideline as PCB routing from Host Controller to Level Shifter.

- Series Termination and Placement if series termination resistors are to be used, the suggested values are 22  $\Omega$  to 33  $\Omega$ . The termination resistors on the card side of the level shifter should be placed close to the card socket as shown in Figure 2.

- PCB trace separation the trace separation impedance should follow the guideline as PCB routing from Host Controller to Level Shifter.

- Trace Routing when routing the PCB traces, it is critical to keep the trace width

the same to keep the trace impedance constant from the driver to the receiver. Any

trace width deviation creates impedance mismatch and creates signal reflection.

Avoid using 90-degree angle and use 45-degree bend when the trace must be routed

perpendicularly.

- The total capacitance between the level shifter and the card should follow the recommendation in the SD Physical Layer specification[1].

#### NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

Table 1. I/O driver design target

| Drive type           | Symbol                             | Driver rise/fa | Condition |      |       |       |

|----------------------|------------------------------------|----------------|-----------|------|-------|-------|

|                      |                                    | Min            | Тур       | Max  | Units | CL    |

| Type B for<br>UHS104 | T <sub>R</sub> B, T <sub>F</sub> B | 0.40           | 0.88      | 1.32 | ns    | 15 pF |

| Type B for UHS50     | T <sub>R</sub> B, T <sub>F</sub> B | 0.70           | 1.83      | 2.75 | ns    | 30 pF |

<sup>•</sup> PCB Trace length matching - to minimize the skew between traces, route them with the same length.

#### 3 Conclusion

Proper PCB layout is critical for the successful operation of NT4858/NVT4557/NVT4558. All high-speed PCB rules, techniques, component placement and trace routing must be followed and taken into consideration during the PCB layout phase.

#### 4 References

[1] SD Specifications, Part 1, Physical Layer Specification; version 3.01; February 18, 2010

#### NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

# 5 Legal information

#### 5.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own tick.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="mailto:PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 5.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

${f NXP}$  — wordmark and logo are trademarks of NXP B.V.

AN13158

# NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

| Tables  |                             |         |                        |  |  |  |

|---------|-----------------------------|---------|------------------------|--|--|--|

| Tab. 1. | I/O driver design target5   |         |                        |  |  |  |

| Figur   | res                         |         |                        |  |  |  |

| Fig. 1. | Bypass capacitor placement3 | Fig. 2. | Termination resistors4 |  |  |  |

# NVT4557/NVT4558/NVT4858 voltage-level translator layout guideline

### **Contents**

| 1   | Introduction                             | 3            |

|-----|------------------------------------------|--------------|

| 2   | NVT4557/4558/4858 voltage-level          | _            |

|     | translator layout guidelines             | 3            |

| 2.1 | Power and ground                         | 3            |

| 2.2 | SD and SIM signals from host to level    |              |

|     | shifter                                  | 3            |

| 2.3 | SD and SIM signals from level shifter to |              |

|     | card socket                              | 4            |

| 3   | Conclusion                               | 5            |

| 4   | References                               | <del>5</del> |

| 5   | Legal information                        | é            |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.