# Freescale Semiconductor Application Note

Document Number: AN4179 Rev. 0, 7/2010

# How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64

by: Saurabh Jhamb, Tanya Malik

Reference Design and Applications Engineering

Microcontroller Solutions Group

# 1 Introduction

This document describes a driver for the LCD. This LCD driver allows the user to customize glass requirements with the MCU's LCD module. This driver is tested for the microcontroller demo board MC9S08GW64 (TWR-S08GW64).

The software architecture is designed to provide seamless migration between these devices. This document is intended to be used by all software development engineers and test engineers who has to use the MCUs with the LCD.

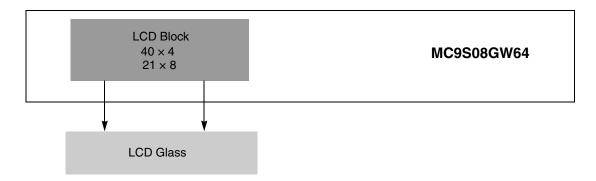

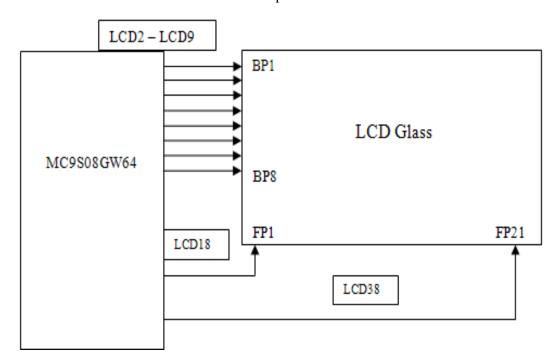

Figure 1 shows the block diagram for the LCD. The MC9S08GW64 contains 44 pins for LCD frontplane and backplane operation that are totally configurable. Therefore, any pin can be configured for use with either the frontplane or the backplane.

#### **Contents**

| 1 | Introduction |                                           |  |  |  |  |  |  |  |

|---|--------------|-------------------------------------------|--|--|--|--|--|--|--|

| 2 | Har          | Hardware interface description            |  |  |  |  |  |  |  |

|   | 2.1          | Frontplane and backplane pin connections2 |  |  |  |  |  |  |  |

|   | 2.2          | Voltage pin connections                   |  |  |  |  |  |  |  |

|   | 2.3          | Frontplane and backplane configuration 3  |  |  |  |  |  |  |  |

| 3 | LCI          | O Software                                |  |  |  |  |  |  |  |

|   | 3.1          | LCD software architecture 5               |  |  |  |  |  |  |  |

|   | 3.2          | Hardware Abstraction Layer(HAL)6          |  |  |  |  |  |  |  |

|   | 3.3          | LCD HAL functions                         |  |  |  |  |  |  |  |

| 4 | Inte         | rfacing LCD glass with MC9S08GW64 13      |  |  |  |  |  |  |  |

| 5 | Opt          | ions for V <sub>LL3</sub>                 |  |  |  |  |  |  |  |

| 6 | Cor          | nclusion                                  |  |  |  |  |  |  |  |

| 7 | Ref          | erences                                   |  |  |  |  |  |  |  |

#### Hardware interface description

Figure 1. LCD block diagram

# 2 Hardware interface description

Table 1 describes the LCD pins and their directions.

$V_{CAP2}$

**Pins** Direction Description LCD[43:0] Output LCD data pins User can configure these pins as frontplane or backplane.  $V_{LL1}$ Output LCD bias voltage  $V_{LL2}$ Output LCD bias voltage  $V_{LL3}$ Input LCD bias voltage See Section 5, "Options for V<sub>LL3</sub>," for more details.  $V_{LL3_2}$ Provides current enhancement at VII3 Input Note: This pin must be shorted with  $V_{LL3}$ .  $V_{CAP1}$ N/A Provides storage capacitance for LCD operation on internal charge pump mode.

Table 1. LCD pin description

# 2.1 Frontplane and backplane pin connections

N/A

These pin connections identify the number of backplanes and frontplanes supported in the LCD glass and connect each LCD glass pin to the respective LCD pin at the MC9S08GW64 MCU.

#### NOTE

In the LCD software driver configuration, the number of LCD pins in a MCU that connect to the backplane of the LCD glass must be configured as backplane.

# 2.2 Voltage pin connections

Add a capacitor on the  $V_{LL3}$  pin to filter noise from the  $V_{DD}$  input and on  $V_{LL1}$ ,  $V_{LL2}$ ,  $V_{CAP1}$ , and  $V_{CAP2}$  pins for the LCD operation in charge pump mode. No capacitor is required for the LCD operation in resistor bias mode on  $V_{LL1}$ ,  $V_{LL2}$ ,  $V_{CAP1}$ , and  $V_{CAP2}$  pins

# 2.3 Frontplane and backplane configuration

# 2.3.1 LCD pin enable registers (LCDPENn)

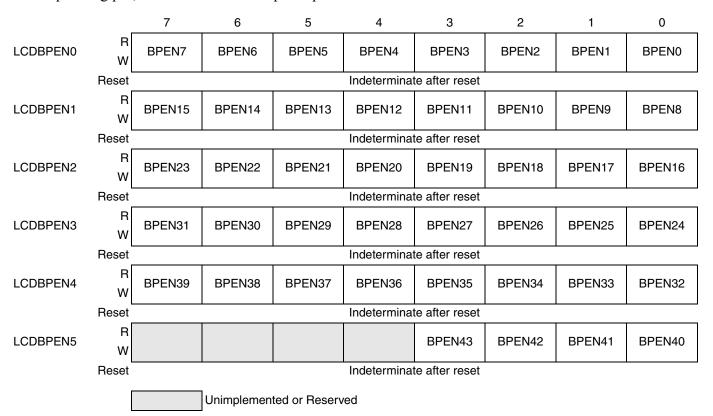

These registers specify the number of pins used for the LCD display.

|         |        | 7                         | 6                         | 5     | 4            | 3             | 2     | 1     | 0     |

|---------|--------|---------------------------|---------------------------|-------|--------------|---------------|-------|-------|-------|

| LCDPEN0 | R<br>W | PEN7                      | PEN6                      | PEN5  | PEN4         | PEN3          | PEN2  | PEN1  | PEN0  |

|         | Reset  |                           |                           |       | Indeterminat | e after reset |       |       |       |

| LCDPEN1 | R<br>W | PEN15                     | PEN14                     | PEN13 | PEN12        | PEN11         | PEN10 | PEN9  | PEN8  |

|         | Reset  |                           |                           |       | Indeterminat | e after reset |       |       |       |

| LCDPEN2 | R<br>W | PEN23                     | PEN22                     | PEN21 | PEN20        | PEN19         | PEN18 | PEN17 | PEN16 |

|         | Reset  | Indeterminate after reset |                           |       |              |               |       |       |       |

| LCDPEN3 | R<br>W | PEN31                     | PEN30                     | PEN29 | PEN28        | PEN27         | PEN26 | PEN25 | PEN24 |

|         | Reset  |                           | Indeterminate after reset |       |              |               |       |       |       |

| LCDPEN4 | R<br>W | PEN39                     | PEN38                     | PEN37 | PEN36        | PEN35         | PEN34 | PEN33 | PEN32 |

|         | Reset  | Indeterminate after reset |                           |       |              |               |       |       |       |

| LCDPEN5 | R<br>W |                           |                           |       |              | PEN43         | PEN42 | PEN41 | PEN40 |

|         | Reset  |                           | Indeterminate after reset |       |              |               |       |       |       |

|         |        | Unimplemented or Reserved |                           |       |              |               |       |       |       |

Figure 2. LCDPENn registers

Table 2. LCDPEN[5:0] field descriptions

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PEN[43:0] | LCD Pin Enable—The PEN[43:0] bit enables the LCD[43:0] pin for the LCD operation. Each LCD[43:0] pin can be configured as a backplane or a frontplane based on the corresponding BPEN[n] bit in the Backplane Enable Register (LCDBPEN[5:0]). If LCDEN = 0, these bits have no effect on the state of the I/O pins. Set PEN[43:0] bits before LCDEN is set.  0 LCD operation disabled 1 LCD operation enabled |

Hardware interface description

# 2.3.2 Backplane enable registers

These registers specify the number of pins used as backplane. If the BPEN bits are cleared for a corresponding pin, then it acts as a frontplane pin.

Figure 3. LCDBPEN[5:0] registers

Table 3. LCDBPEN[5:0] field descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCDBPEN[43:0] | Backplane Enable—The BPEN[43:0] bit configures the LCD[43:0] pin to operate as an LCD backplane or LCD frontplane. If LCDEN = 0, these bits have no effect on the state of the I/O pins. It is recommended to set BPEN[43:0] bits before LCDEN is set.  0 Frontplane operation enabled  1 Backplane operation enabled |

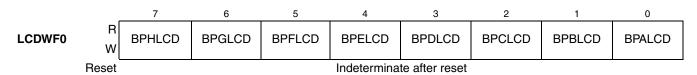

# 2.3.3 LCD waveform register

Figure 4. LCDWF0 register

\_ . . .

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

#### **NOTE**

There are 64 LCD waveform registers LCDWF0 - LCDWF63. For more information, refer to the *MC9S08GW64 Reference Manual* (document MC9S08GW64RM).

Table 4. LCDWF field descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BP[x]LCD[y] | Segment on frontplane operation — If the LCD[x] pin is enabled and configured to operate as a frontplane, the BP[y]LCD[x] bits in the LCDWF registers controls the on/off state for the LCD segment connected between LCD[x] and BP[y]. BP[y] corresponds to LCD[43:0] pin enabled and configured to operate as a backplane that is active in phase[y]. Asserting BP[y]LCD[x] displays (turns on) the LCD segment connected between LCD[x] and BPp[y].  0 LCD segment off 1 LCD segment on Segment on backplane operation — If the LCD[x] pin is enabled and configured to operate as a backplane, the BP[y] LCD[x] bit in the LCDWF registers controls the phase (A-H) in which the LCD[x] pin is active. Backplane phase assignment is done using the method.  0 LCD BP[x] inactive for LCD[y] 1 LCD BP[x] active for LCD[y] |

# 3 LCD Software

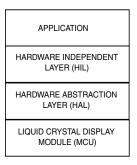

#### 3.1 LCD software architecture

Figure 5. LCD software architecture

#### 3.1.1 Hardware abstraction layer

The hardware abstraction layer is defined as a collection of software components that directly access hardware resources. In this layer, the LCD driver defines macros and functions that configure the custom glass requirements in the LCD module registers.

## 3.1.2 Hardware independent layer

The hardware independent layer is defined as a collection of software components that access hardware resources through HAL. Peripheral drivers are implemented in this layer.

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

## 3.2 Hardware Abstraction Layer(HAL)

The HAL module defines the macros and functions needed to match the custom glass hardware specifications with the MCU LCD registers. This information is obtained from each custom glass specification. The changes to these macros are performed through modifications on the macro definitions located in the *lcd.h* header file. The user functions are located in *lcd.c*

The user is responsible for providing correct definitions for these hardware access macros. Descriptions of the individual macros and examples of their definitions are given below.

# 3.2.1 LCD\_NO\_OF\_BACK\_PLANES

The LCD\_NO\_OF\_BACK\_PLANES macro defines the number of backplane electrodes on the custom glass. The duty ratio of the waveforms generated by the LCD module is 1/ (\_LCDBACKPLANES). This module supports values from 1–8.

## 3.2.2 LCD CLOCK

The LCD\_CLOCK macro defines the LCD module clock source. The available clocks are the internal (also called alternate) clock or the external clock of 32.768 kHz. The supported clock range is from 30 kHz to 39.053 kHz.

- LCD CLOCK EXT—Selects external clock source

- LCD CLOCK ALT—Selects alternate clock source

Example: #define LCD\_CLOCK LCD\_CLOCK\_EXT

# 3.2.3 LCD VSUPPLY

The LCD\_VSUPPLY macro defines whether the LCD module power supply is internal or external. These device sources change in each device. Supply sources for the MC9S08GW64 are:

- LCD VLL2 FROM VDD—Drive  $V_{LL2}$  internally from  $V_{DD}$

- LCD VLL3 FROM VDD—Drive  $V_{LL3}$  internally from  $V_{DD}$

- LCD\_VLL1\_FROM\_VLCD—Drive  $V_{LL1}$  internally from  $V_{LCD}$

- LCD\_VLL3\_FROM\_EXT—Drive V<sub>LL3</sub> externally Or V<sub>IREG</sub>

Example: #define LCD\_VSUPPLY LCD\_VLL3\_FROM\_VDD

# 3.2.4 LCD\_CLOCK\_PRESCALER

This macro defines the LCD clock pre-scaler, which in combination with the number of backplanes of the LCD determines the LCD frame frequency.

The LCD frame frequency is the number of times the LCD is energized per second. The LCD module frame frequency must be selected to prevent the LCD display from flickering (LCD module frame frequency is too low) or ghosting (LCD module frame frequency is too high). To avoid these conditions, an LCD module frame frequency in the range of 28 Hz to 58 Hz is required.

Table 5 and Table 6 shows the LCD frame frequency calculations and have LCD clock inputs as ~32.786 kHz and ~ 39.063 kHz, respectively.

Table 5. LCD frame frequency calculation at ~32.786kHz

| <b>Duty Cycle</b> | 1/1  | 1/2  | 1/3  | 1/4  | 1/5  | 1/6  | 1/7  | 1/8  |

|-------------------|------|------|------|------|------|------|------|------|

| Υ                 | 16   | 8    | 5    | 4    | 3    | 3    | 2    | 2    |

| LCLK[2:0]         |      |      |      |      |      |      |      |      |

| 0                 | 64   | 64   | 68.3 | 64   | 68.3 | 56.9 | 73.1 | 64   |

| 1                 | 51.2 | 51.2 | 54.6 | 51.2 | 54.6 | 45.5 | 58.5 | 51.2 |

| 2                 | 42.7 | 42.7 | 45.5 | 42.7 | 45.5 | 37.9 | 48.8 | 42.7 |

| 3                 | 36.6 | 36.6 | 39   | 36.6 | 39   | 32.5 | 41.8 | 36.6 |

| 4                 | 32   | 32   | 34.1 | 32   | 34.1 | 28.4 | 36.6 | 32   |

| 5                 | 28.4 | 28.4 | 30.3 | 28.4 | 30.3 | 25.3 | 32.5 | 28.4 |

| 6                 | 25.6 | 25.6 | 27.3 | 25.6 | 27.3 | 22.8 | 29.3 | 25.6 |

| 7                 | 23.3 | 23.3 | 24.8 | 23.3 | 24.8 | 20.7 | 26.6 | 23.3 |

Table 6. LCD frame frequency calculation at ~39.063

| <b>Duty Cycle</b> | 1/1  | 1/2  | 1/3  | 1/4  | 1/5  | 1/6  | 1/7  | 1/8  |

|-------------------|------|------|------|------|------|------|------|------|

| Y                 | 16   | 8    | 5    | 4    | 3    | 3    | 2    | 2    |

| LCLK[2:0]         |      |      |      |      |      |      |      |      |

| 0                 | 76.3 | 76.3 | 81.4 | 76.3 | 81.4 | 67.8 | 87.2 | 76.3 |

| 1                 | 61   | 61   | 65.1 | 61   | 65.1 | 54.3 | 69.8 | 61   |

| 2                 | 50.9 | 50.9 | 54.3 | 50.9 | 54.3 | 45.2 | 58.1 | 50.9 |

| 3                 | 43.6 | 43.6 | 46.5 | 43.6 | 46.5 | 38.8 | 49.8 | 43.6 |

| 4                 | 38.1 | 38.1 | 40.7 | 38.1 | 40.7 | 33.9 | 43.6 | 38.1 |

| 5                 | 33.9 | 33.9 | 36.2 | 33.9 | 36.2 | 30.1 | 38.8 | 33.9 |

| 6                 | 30.5 | 30.5 | 32.6 | 30.5 | 32.6 | 27.1 | 34.9 | 30.5 |

| 7                 | 27.7 | 27.7 | 29.6 | 27.7 | 29.6 | 24.7 | 31.7 | 27.7 |

Example: #define LCD\_CLOCK\_PRESCALER 0

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0 7 Freescale Semiconductor

# 3.2.5 LCD\_CHARGE\_PUMP\_SELECT

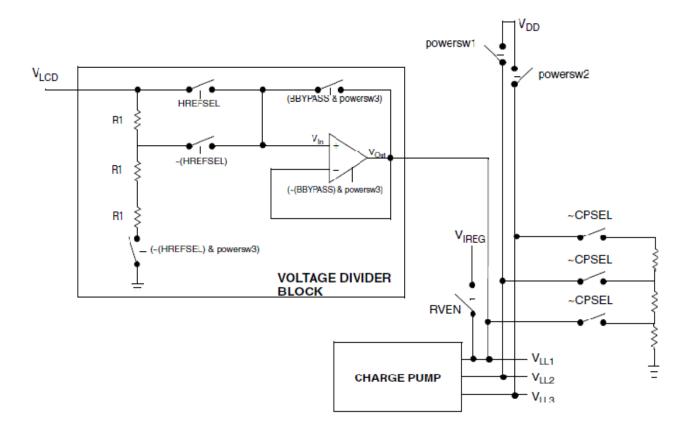

The LCD charge pump selector macro defines the type of supply for the LCD voltages  $V_{LL1}$ ,  $V_{LL2}$ , and  $V_{LL3}$ . The LCD module provides two options for the supply voltage: resistor network or charge pump (Figure 6).

- LCD CHARGE PUMP DISABLE—Selects the resistor network

- LCD CHARGE PUMP ENABLE—Selects the charge pump

Example: #define LCD\_CHARGE\_PUMP\_SELECT LCD\_CHARGE\_PUMP\_ENABLE

| VSUPPLY[1:0] | Configuration                                                                                | powersw1 | powersw2 | powersw3 |

|--------------|----------------------------------------------------------------------------------------------|----------|----------|----------|

| 00           | Drive $V_{LL2}$ internally from $V_{DD}$                                                     | 1        | 0        | 0        |

| 01           | Drive $V_{LL3}$ internally from $V_{DD}$                                                     | 0        | 1        | 0        |

| 10           | Drive $V_{LL1}$ internally from the $V_{LCD}$ pin                                            | 0        | 0        | 1        |

| 11           | Drive $V_{LL3}$ externally from $V_{DD}$<br>Or<br>Drive $V_{LL1}$ internally from $V_{IREG}$ | 0        | 0        | 0        |

Figure 6. LCD Charge Pump and VLCD Voltage Divider Block Diagram

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

### 3.2.6 LCD LOAD ADJUST

The load adjust macro configures the LCD module to manage a different LCD glass capacitance. The capacitance of the LCD depends on the custom glass. The value written in this macro is related to the type of voltage source selected (resistor network or charge pump). The results for the different possible combinations of LCD\_LOAD\_ADJUST and LCD\_CHARGE\_PUMP\_SELECT (0—resistor network, 1—charge pump) for MC9S08GW64 are shown in Table 7.

| LCD_LOAD_ADJUST | LCD_CHARGE_PUMP_SELECT=1 | LCD_CHARGE_PUMP_SELECT=0 |

|-----------------|--------------------------|--------------------------|

| 0               | 8000pF                   | 2000pF                   |

| 1               | 6000pF                   | 2000pF                   |

| 2               | 4000pF                   | 8000pF                   |

| 3               | 2000pF                   | 8000pF                   |

Table 7. LCD load adjust values

For more information, refer to the MC9S08GW64 Reference Manual (document MC9S08GW64RM).

## 3.2.7 CONFIG\_LCD\_MODE

This macro configures the 29 pin LCD with 21 frontplanes and 8 backplanes. The user needs to change the configuration depending upon the LCD used and the connection of the LCD with the MCU.

```

#define CONFIG LCD MODE

LCDPEN0 = 0xFC; /*Enables the respective pins of the MCU connected with the LCD glass */

LCDPEN1 = 0x03;

LCDPEN2 = 0xFC;

LCDPEN3 = 0xFF;

LCDPEN4 = 0x7F;

LCDPEN5 = 0x00;

LCDBPEN0 = 0xFC;

/*It enables the respective LCD pin as backplane*/

LCDBPEN1 = 0x03;

LCDBPEN2 = 0x00;

LCDBPEN3 = 0 \times 00;

LCDBPEN4 = 0x00;

LCDBPEN5 = 0 \times 00;

LCDPIN1 = 0x01;

/*It is used to enable the required segments*/

LCDPIN2 = 0x02;

LCDPIN3 = 0x04;

LCDPIN4 = 0x08;

LCDPIN5 = 0x10;

```

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

```

LCDPIN6 = 0x20;

LCDPIN7 = 0x40;

LCDPIN8 = 0x80;

```

# 3.2.8 LCD\_ALLFP\_OFF

This macro is used to turn off all the segments of the custom glass.

## 3.2.9 LCD ALLFP ON

This macro is used to turn on all the segments of the custom glass.

## 3.3 LCD HAL functions

# 3.3.1 LCDFindChar()

#### **Description:**

Finds the position of the given character in the character table defined in *lcd.h*

#### **Prototype:**

```

unsigned char LCDFindChar(unsigned char character)

```

#### Input parameters:

character—The character whose position is to be found.

#### Return value:

None

#### **Typical usage:**

```

LCDFindChar('A');

```

# 3.3.2 LCDPutChar()

#### **Description:**

It puts the character in the LCD RAM register and the character is displayed on the LCD glass at the position specified.

#### **Prototype:**

```

void LCDPutChar(unsigned char character, unsigned char digit)

```

#### **Input parameters:**

```

character—The character to be displayed.

```

digit—The position on the LCD glass.

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

#### Return value:

None

#### Typical usage:

LCDPutChar ('A',2);

# 3.3.3 LCDWriteSegment()

#### **Description:**

It displays the respective symbol on the LCD glass.

#### **Prototype:**

void LCDWriteSegment(enum symbol s, unsigned char num)

#### **Input parameters:**

s—The symbol to be displayed.

num—The position on the LCD glass.

#### **Return value:**

None

#### **Typical usage:**

LCDWriteSegment(TIME, 2);

# 3.3.4 LCDClearSegment()

#### **Description:**

It clears the respective symbol on the LCD glass.

#### **Prototype:**

void LCDClearSegment(enum symbol s, unsigned char num)

#### **Input parameters:**

s—The symbol to be cleared.

num—The position on the LCD glass.

#### **Return value:**

None

#### **Typical usage:**

LCDClearSegment(TIME, 2);

# 3.3.5 LCDClearSegs()

#### **Description:**

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

It clears all the segments.

#### **Prototype:**

void LCDClearSegs(void)

#### **Input parameters:**

None

#### Return value:

None

#### **Typical usage:**

LCDClearSegs();

# 3.3.6 LCDClearDigit()

#### **Description:**

It clears all the digits.

#### **Prototype:**

void LCDClearDigit()

#### **Input parameters:**

None

#### Return value:

None

# **Typical usage:**

LCDClearDigit();

# 3.3.7 **LCDTest()**

#### **Description:**

It enables all the segments on the LCD used to test the LCD.

#### **Prototype:**

void LCDTest (void)

#### **Input parameters:**

None

#### Return value:

None

#### Typical usage:

LCDTest();

# 4 Interfacing LCD glass with MC9S08GW64

This section describes an example of interfacing the LCD glass (21 x 8) with the MC9S08GW64. The LCD module of the MCU is configured in charge pump enable mode, and drives  $V_{LL3}$  pin from  $V_{DD}$  supply. Figure 7 shows the hardware connections for this example.

Figure 7. Hardware connections for interfacing LCD glass with MC9S08GW64

Follow the instructions below to configure the LCD block of the MC9S08GW64 to operate with an LCD glass, and to operate in charge pump mode with  $V_{LL3}$  driven by  $V_{DD}$ .

1. Select the following configuration in *lcd.h*.

```

#define LCD_NO_OF_BACK_PLANES 8

#define LCD_CLOCK LCD_CLOCK_EXT

#define LCD_CLOCK_PRESCALER 0

#define LCD_CHARGE_PUMP_SELECT LCD_CHARGE_PUMP_ENABLE

#define LCD_LOAD_ADJUST 3

```

#### NOTE

- For a 3V LCD glass select the configuration as #define LCD\_VSUPPLY LCD\_VLL3\_FROM\_VDD

- For a 5V LCD glass select the configuration as  $\#define\ LCD\_VSUPPLY\ LCD\ VLL2\ FROM\ VDD$

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

#### Interfacing LCD glass with MC9S08GW64

2. Depending upon the connection between the MCU LCD pins and the LCD glass pins, check the following defines.

```

/* Pin 1 of LCD glass connected to LCD2

#define LCDPIN1

LCDWF2

#define LCDPIN2

LCDWF3

/* Pin 2 of LCD glass connected to LCD3

*/

#define LCDPIN3

/* Pin 3 of LCD glass connected to LCD4

*/

LCDWF4

#define LCDPIN4

/* Pin 4 of LCD glass connected to LCD5

LCDWF5

*/

#define LCDPIN5

/* Pin 5 of LCD glass connected to LCD6

LCDWF6

*/

/* Pin 6 of LCD glass connected to LCD7

#define LCDPIN6

LCDWF7

* /

#define LCDPIN7

/* Pin 7 of LCD glass connected to LCD8

* /

LCDWF8

#define LCDPIN8

/* Pin 8 of LCD glass connected to LCD9

* /

LCDWF9

/* Pin 9 of LCD glass connected to LCD18 */

#define LCDPIN9

LCDWF18

/* Pin 10 of LCD glass connected to LCD19 */

#define LCDPIN10

LCDWF19

#define LCDPIN11

/* Pin 11 of LCD glass connected to LCD20 */

LCDWF20

#define LCDPIN12

/* Pin 12 of LCD glass connected to LCD21 */

LCDWF21

#define LCDPIN13

LCDWF22

/* Pin 13 of LCD glass connected to LCD22 */

#define LCDPIN14

/* Pin 14 of LCD glass connected to LCD23 */

LCDWF23

#define LCDPIN15

/* Pin 15 of LCD glass connected to LCD24 */

LCDWF24

/* Pin 16 of LCD glass connected to LCD25 */

#define LCDPIN16

LCDWF25

#define LCDPIN17

/* Pin 17 of LCD glass connected to LCD26 */

LCDWF26

#define LCDPIN18

LCDWF27

/* Pin 18 of LCD glass connected to LCD27 */

#define LCDPIN19

/* Pin 19 of LCD glass connected to LCD28 */

LCDWF28

#define LCDPIN20

/* Pin 20 of LCD glass connected to LCD29 */

LCDWF29

#define LCDPIN21

/* Pin 21 of LCD glass connected to LCD30 */

LCDWF30

#define LCDPIN22

LCDWF31

/* Pin 22 of LCD glass connected to LCD31 */

#define LCDPIN23

/* Pin 23 of LCD glass connected to LCD32 */

LCDWF32

#define LCDPIN24

/* Pin 24 of LCD glass connected to LCD33 */

T.CDWF33

#define LCDPIN25

LCDWF34

/* Pin 25 of LCD glass connected to LCD34 */

#define LCDPIN26

/* Pin 26 of LCD glass connected to LCD35 */

LCDWF35

#define LCDPIN27

/* Pin 27 of LCD glass connected to LCD36 */

LCDWF36

/* Pin 28 of LCD glass connected to LCD37 */

#define LCDPIN28

LCDWF37

#define LCDPIN29

LCDWF38

/* Pin 29 of LCD glass connected to LCD38 */

```

3. Depending upon the backplanes and frontplanes to be used, verify the settings of CONFIG\_LCD\_MODE. The macro is used to enable the LCD pins, enable the frontplanes and enable the backplanes as shown:

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

```

LCDPEN2 = 0xFC;

LCDPEN3 = 0xFF;

LCDPEN4 = 0x7F;

LCDPEN5 = 0x00;

LCDBPEN0 = 0xFC;

/*It enables the respective LCD pin as backplane*/

LCDBPEN1 = 0x03;

LCDBPEN2 = 0 \times 00;

LCDBPEN3 = 0x00;

LCDBPEN4 = 0 \times 00;

LCDBPEN5 = 0 \times 00;

LCDPIN1 = 0x01;

/*It is used to enable the required segments*/

LCDPIN2 = 0x02;

LCDPIN3 = 0x04;

LCDPIN4 = 0x08;

LCDPIN5 = 0x10;

LCDPIN6 = 0x20;

LCDPIN7 = 0x40;

LCDPIN8 = 0x80;

}

```

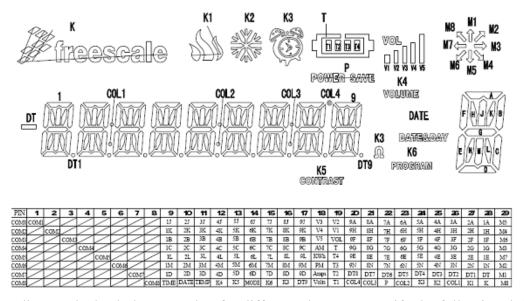

4. Following is the snapshot of the data sheet of the LCD used in TWR-S08GW64.

Depending on the backplanes used to for different characters, verify the following defines.

```

#define LCD_SEG_NONE 0x00  /* no segment is selected */

#define LCD_SEG_J 0x01

#define LCD_SEG_K 0x02

```

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

#### Interfacing LCD glass with MC9S08GW64

```

#define LCD SEG B

0 \times 04

#define LCD SEG C

0x08

#define LCD SEG L

0x10

#define LCD SEG M

0x20

#define LCD SEG D

0x40

#define LCD SEG SP

0x80

#define LCD SEG A

0x01

#define LCD SEG H

0x02

#define LCD SEG F

0x04

#define LCD SEG G

0x08

#define LCD SEG E

0x10

#define LCD SEG N

0x20

#define LCD SEG SP2

0x40

#define LCD SEG SP3

0x80

0x01

#define LCD SEG M5

#define LCD SEG M4

0x02

#define LCD SEG M6

0x04

#define LCD SEG M3

0x08

#define LCD SEG M7

0x10

#define LCD_SEG_M2

0x20

#define LCD SEG M1

0 \times 40

#define LCD SEG M8

0x80

```

5. Verify the symbols to be used, which are declared as shown

```

enum symbol { TIME, DT, DATE, FREESCALE, FIRE, TEMP, SNOWFLAKE, VOLUME, ALARM, T, P, CONTRAST, MODE, AM, PM, OM, KWH, AMPS, VOLTS, PROGRAM, VOL, DTx, COLx, Vx, Tx, Mx};

```

6. Open *lcd.c* and verify the structure <code>lcd\_char\_table[]</code>. This table defines the segments required to display the characters and digits.

**For example:** To display 0 on the LCD, the following setting is required in the LCD used in TWR-S08GW64

```

{

LCD_SEG_B | LCD_SEG_C | LCD_SEG_D,

LCD_SEG_E | LCD_SEG_F | LCD_SEG_A

},

```

7. This sample code can be used to test the driver.

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

```

LCD_ALLFP_ON

/*All segments are off*/

LCD_ALLFP_OFF

lcd_PrintString("hello");

```

# 5 Options for V<sub>LL3</sub>

Table 8 describes the configurations for V<sub>LL3</sub> in MC980SGW64.

#### NOTE

V<sub>LL3</sub> and V<sub>DD</sub> if different at power ramp, will cause current leakage.

Table 8. V<sub>LL3</sub> configurations for LCD

| Configuration                                                                              | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>LL3</sub> connected to external supply                                              | This configuration applies if the user:  • Uses any of the 44 LCD pins as a full complementary digital GPIO.  • Varies V <sub>DD</sub> through board regulator to enable the LCD contrast control feature.  • Selects register bias mode or charge pump operating mode.                                                                                                                                                                                                                                                                                                                    |

| V <sub>LL3</sub> connected to V <sub>DD</sub> internally                                   | <ul> <li>This configuration applies if the user:</li> <li>Uses any of the 44 LCD pins as a full complementary digital GPIO. GPIOs toggling as outputs must be configured as open drain. User can use digital input functions for these GPIOs.</li> <li>Varies V<sub>DD</sub> through board regulator to enable the LCD contrast control feature.</li> <li>Selects register bias mode or charge pump operating mode.</li> </ul>                                                                                                                                                             |

| V <sub>LL3</sub> connected to an external independent source through potentiometer network | <ul> <li>This configuration applies if the user:</li> <li>Uses all 44 pins as LCD pins. User can also use digital input functions for GPIOs.</li> <li>Varies V<sub>DD</sub> through the external potentiometer to control the LCD contrast.</li> <li>Selects the preferred charge pumped mode. If register bias mode is selected then the user must ensure that the potentiometer resistance is less than the register bias network values selected by setting LCDSUPPLY_LADJ bits. This is required to avoid a drop in V<sub>LL3</sub> if internal register bias is activated.</li> </ul> |

# 6 Conclusion

This driver provides a software interface between the custom glass pinout and the LCD module in low-power Freescale microcontrollers. Minimal changes are required to customize an LCD application. The user must meet specified hardware requirements. These routines are reliable platforms to migrate between the various families and reduces development time when using Freescale products.

# 7 References

MC9S08GW64 Reference Manual (document: MC9S08GW64RM)

How to Interface and Drive a 3V or 5V LCD Glass with MC9S08GW64, Rev. 0

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:** Freescale Semiconductor, Inc. Technical Information Center, EL516

2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org © Freescale Semiconductor, Inc. 2010. All rights reserved.

Document Number: AN4179

Rev. 0 7/2010